সাধারণত, সম্পূর্ণ বিয়োগকারক সর্বাধিক ব্যবহৃত এবং অপরিহার্য সমন্বিত যুক্তিযুক্ত সার্কিট । এটি একটি প্রাথমিক বৈদ্যুতিন ডিভাইস, দুটি বাইনারি সংখ্যার বিয়োগ সঞ্চালনের জন্য ব্যবহৃত হয়। পূর্ববর্তী নিবন্ধে, ইতিমধ্যে আমরা এর প্রাথমিক তত্ত্বটি দিয়েছি অর্ধ সংযোজক এবং একটি পূর্ণ সংযোজক যা গণনার জন্য বাইনারি সংখ্যা ব্যবহার করে। তেমনি, পূর্ণ বিয়োগকারক বিয়োগের জন্য 0,1 এর মতো বাইনারি অঙ্কগুলি ব্যবহার করে। এর সার্কিটটি যুক্তি গেটগুলি যেমন ওআর, প্রাক্তন-ওআর, ন্যানড গেট দিয়ে তৈরি করা যেতে পারে। এই বিয়োগকারকের ইনপুটগুলি হ'ল এ, বি, বিন এবং আউটপুটগুলি ডি, বাউট।

এই নিবন্ধটি একটি পূর্ণ-সাবট্রেক্টর তত্ত্বের ধারণা দেয় যা একটি সাবট্রাক্টর কী হিসাবে প্রাঙ্গনে গঠিত, লজিক গেটস, ট্রুথ টেবিল ইত্যাদির সাথে নকশা করা এই প্রবন্ধটি ইঞ্জিনিয়ারিং শিক্ষার্থীদের জন্য দরকারী যারা এইচডিএল প্রাকটিক্যাল ল্যাবটিতে এই বিষয়গুলি দিয়ে যেতে পারেন।

সাবট্রাক্টর কী?

বাইনারি অঙ্কগুলি বিয়োগ সাবট্রাক্টর সার্কিটের সাহায্যে করা যেতে পারে। এটি এক ধরণের সম্মিলিত লজিক সার্কিট, 0 এবং 1 এর মতো দুটি বাইনারি সংখ্যার বিয়োগ করতে ব্যবহৃত হয়। 0 থেকে 0 বা 0 থেকে 1 পর্যন্ত বাইনারি অঙ্কের বিয়োগের ফলে ফলাফলের পরিবর্তন হয় না, 1 থেকে 1 এর বিয়োগটি 0 হিসাবে ফলাফল করবে তবে 1 থেকে 0 এর বিয়োগের জন্য needsণ নেওয়া দরকার।

উদাহরণস্বরূপ, দুই বিট সাবট্রাক্টর সার্কিট এ এবং বি এর মতো দুটি ইনপুট অন্তর্ভুক্ত করে তবে ফলাফলগুলি পার্থক্য এবং orrowণ গ্রহণ করে। এই সার্কিটটি ইনভার্টারগুলির সাথে সংযোজকগুলির সাথে তৈরি করা যেতে পারে যা এফএর পূর্ববর্তী পর্যায়ে প্রতিটি ডেটা ইনপুট পাশাপাশি ধার (বিন) ইনপুট থাকে।

সাবট্রাক্টরগুলি অর্ধ বিয়োগকার এবং সম্পূর্ণ সাবট্রাক্টরের মতো দুটি ধরণের শ্রেণিবদ্ধ করা হয়। এখানে আমরা সম্পূর্ণ বিয়োগকারকে নিয়ে আলোচনা করছি।

পূর্ণ বিয়োগকারক কী?

এটি একটি বৈদ্যুতিন ডিভাইস বা লজিক সার্কিট যা দুটি বাইনারি অঙ্কের বিয়োগফল সম্পাদন করে। এটি ডিজিটাল ইলেক্ট্রনিক্সে ব্যবহৃত একটি যুক্ত যৌক্তিক লজিক সার্কিট। অনেক সংযুক্ত সার্কিট পাওয়া যায় ইন্টিগ্রেটেড সার্কিট প্রযুক্তি যথা সংযোজক, এনকোডার, ডিকোডার এবং একাধিক প্লেয়ার। এই নিবন্ধে, আমরা অর্ধ বিয়োগকার এবং সত্য টেবিলের মতো পদগুলি ব্যবহার করে এর নির্মাণ সম্পর্কে আলোচনা করতে যাচ্ছি।

সম্পূর্ণ সাবট্রাক্টর

এর ডিজাইনিং দুটি অর্ধ বিয়োগকার দ্বারা করা যেতে পারে, যার মধ্যে তিনটি ইনপুট যেমন মিনুয়েন্ড, সাবট্রেন্ড এবং ধার করা হয়, ইনপুটগুলির মধ্যে orrowণ বিট দুটি বাইনারি অঙ্কের বিয়োগ থেকে প্রাপ্ত হয় এবং পরবর্তী উচ্চ-অর্ডার জোড়া থেকে বিয়োগ করা হয় বিট, পার্থক্য এবং asণ হিসাবে আউটপুট।

দ্য পূর্ণ বিয়োগকারীর ব্লক ডায়াগ্রাম নীচে প্রদর্শিত হয়। অর্ধ বিয়োগকারকের সর্বাধিক অসুবিধা হ'ল আমরা এই বিয়োগকারীর মধ্যে কোনও orrowণ বিট করতে পারি না। যদিও এর নকশায় আমরা প্রকৃত অর্থে সার্কিটে orrowণ গ্রহণ করতে পারি এবং বাকী দুটি আই / পিএস দিয়ে বিয়োগ করতে পারি। এখানে A হ'ল মিনিট, বি হ'ল সাবট্রেন্ড এবং বিন .ণ গ্রহণ করা হয়েছে Dif ফলাফলগুলি হ'ল ডিফারেন্স (ডিফ) এবং আউট (আউট আউট)। সম্পূর্ণ সাবট্রেক্টর সার্কিট অতিরিক্ত অর্ডার বা দু'টি গেটের সাহায্যে দু'জন সাবট্র্যাক্টর ব্যবহার করে অর্জন করতে পারে।

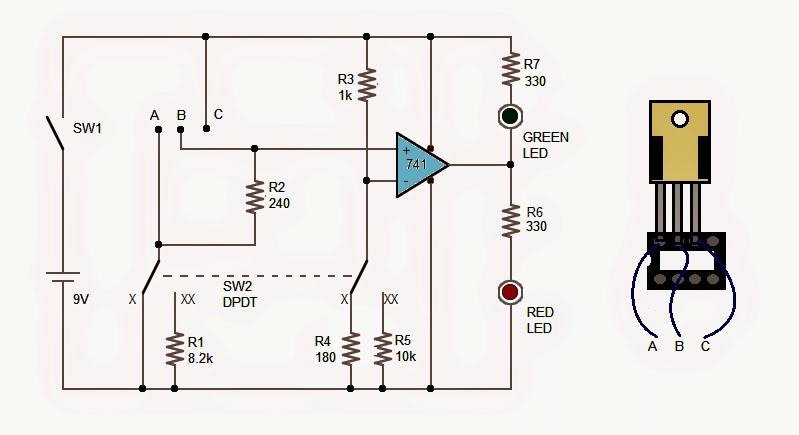

লজিক গেটস সহ সম্পূর্ণ সাবট্রেক্টর সার্কিট ডায়াগ্রাম

দ্য বেসিক গেট ব্যবহার করে পূর্ণ বিয়োগকারীর সার্কিট ডায়াগ্রাম গুলি নিম্নলিখিত ব্লক ডায়াগ্রামে প্রদর্শিত হয়। এই সার্কিটটি দুটি অর্ধ-সাবট্রাক্টর সার্কিট দিয়ে করা যেতে পারে।

প্রাথমিক অর্ধ-সাবট্রেক্টর সার্কিটে, বাইনারি ইনপুটগুলি হ'ল এ এবং বি As যেমন আমরা পূর্ববর্তী অর্ধ-সাবট্রাক্টর নিবন্ধে আলোচনা করেছি, এটি পার্থক্য (ডিফ) এবং orrowণ হিসাবে দুটি আউটপুট উত্পন্ন করবে।

লজিক গেটস ব্যবহার করে সম্পূর্ণ সাবট্রেক্টর

বাম সাবট্রাক্টরের পার্থক্য o / p বাম অর্ধ-সাবট্রেক্টর সার্কিটের দেওয়া হয়। ডান অর্ধেক সাবট্রেক্টর সার্কিটের ইনপুটটিতে ডিফ আউটপুট আরও সরবরাহ করা হয়। আমরা পরের অন্যান্য i / p জুড়ে কিছুটা ধার নিয়েছিলাম bit অর্ধ বিয়োগকারক সার্কিট । আরও একবার এটি ডিফ আউট দেওয়ার পাশাপাশি কিছুটা ধার নেবে। এই বিয়োগকারকের চূড়ান্ত আউটপুট হ'ল ডিফ-আউটপুট।

অন্যদিকে, অর্ধেক সাবট্রাক্টর সার্কিটের উভয় থেকে orrowণ নেওয়া ওআরজিক গেটের সাথে সংযুক্ত। সাবট্রাক্টরের দুটি আউটপুট বিটের জন্য বা যুক্তি দেওয়ার বাইরে, আমরা বিয়োগকারীর বাইরে চূড়ান্ত orrowণ গ্রহণ করি। এমএসবি (একটি উল্লেখযোগ্য বিট) বোঝাতে শেষ orrowণ নেওয়া।

আমরা যদি এর অভ্যন্তরীণ সার্কিট পর্যবেক্ষণ করি, আমরা NAND গেট সহ দুটি অর্ধ সাবট্রেক্টর এবং এক্সওআর গেটের সাথে অতিরিক্ত ওআর গেট দেখতে পাব।

পূর্ণ বিয়োগকারীর সত্যের সারণী

এই বিয়োগকারক সার্কিট দুটি বিটের মধ্যে বিয়োগ সঞ্চালন করে, যার 3- ইনপুট (এ, বি, এবং বিন) এবং দুটি আউটপুট (ডি এবং আউট) থাকে। এখানে ইনপুটগুলি ন্যূনতম, subtrahend, এবং পূর্ববর্তী orrowণ নির্দেশ করে, যেখানে দুটি আউটপুটকে orrowণ / পি এবং পার্থক্য হিসাবে চিহ্নিত করা হয়। নিম্নলিখিত চিত্রটি পূর্ণ-বিয়োগকারীর সত্য সারণীটি দেখায়।

ইনপুটস | আউটপুটস | |||

মাইনুন্ড (এ) | সাবট্রেন্ড (বি) | ধার (বিন) | পার্থক্য (ডি) | ধার (আউট) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | ঘ | ঘ | ঘ |

| 0 | ঘ | 0 | ঘ | ঘ |

| 0 | ঘ | ঘ | 0 | ঘ |

ঘ | 0 | 0 | ঘ | 0 |

| ঘ | 0 | ঘ | 0 | 0 |

ঘ | ঘ | 0 | 0 | 0 |

ঘ | ঘ | ঘ | ঘ | ঘ |

কে-ম্যাপ

সরলকরণ সম্পূর্ণ বিয়োগকারক কে-ম্যাপ উপরের পার্থক্য এবং orrowণ জন্য নীচে প্রদর্শিত হয়।

বিনের পাশাপাশি পার্থক্যের জন্য সমীকরণগুলি নীচে উল্লেখ করা হয়েছে।

পার্থক্যের জন্য প্রকাশটি হ'ল,

D = A’B’Bin + AB’Bin ’+ A’BBin’ + ABBin

ধারের জন্য প্রকাশটি হ'ল,

বাউট = এ'বিন + এ'বিবি + বিবিন

সম্পূর্ণ বিয়োগকারীর সার্কিটের ক্যাসকেডিং

পূর্বে, আমরা এর যেমন নির্মাণ, লজিক গেটস সহ সার্কিট ডায়াগ্রামের একটি ওভারভিউ নিয়ে আলোচনা করেছি। তবে আমরা যদি আরও দুটি বিট সংখ্যা দুটি বিয়োগ করতে চাই, তবে এই বিয়োগকারক সার্কিটটি একক বিট সংখ্যা ক্যাসকেড করতে খুব সহায়ক এবং দুটি বাইনারি সংখ্যারও বিয়োগ করে t এই জাতীয় ক্ষেত্রে, একটি পূর্ণ অ্যাডারের ক্যাসকেড সার্কিট নট লজিক গেটের সাহায্যে ব্যবহৃত হয়। 2 এর পরিপূরক কৌশলটি ব্যবহার করে সম্পূর্ণ সংযোজনকারী থেকে পুরো সাবট্রাক্টরে সার্কিটের রূপান্তরকরণ করা যেতে পারে।

সাধারণত, নট গেট নয়ত একটি ইনভার্টার ব্যবহার করে পূর্ণ সংযোজনকারীর জন্য সাবট্রেন্ড ইনপুটগুলি উল্টান। এই মিনুয়েণ্ড (নন-ইনভার্টেড ইনপুট) এবং সাবট্রেন্ড (ইনভার্টেড ইনপুট) যুক্ত করে, এফএ সার্কিটের এলএসবি (ক্যারি ইনপুট) 1, যার অর্থ লজিক হাই অন্যথায় আমরা 2 এর পরিপূরক কৌশলটি ব্যবহার করে দুটি বাইনারি সংখ্যা বিয়োগ করি। এফএ'র আউটপুট হ'ল ডিফ বিট এবং যদি আমরা চালনাটি উল্টে ফেলি তবে আমরা এমএসবিকে অন্যথায় Bণ নিতে পারি। প্রকৃতপক্ষে, আমরা সার্কিটটি ডিজাইন করতে পারি যাতে আউটপুট লক্ষ করা যায়।

ভেরিলোগ কোড

কোডিং অংশের জন্য প্রথমে আমাদের লজিক সার্কিট ডায়াগ্রামের মডেলিংয়ের কাঠামোগত উপায়টি পরীক্ষা করা দরকার। এর লজিক ডায়াগ্রামটি এ্যান্ড গেট, অর্ধেক বিয়োগকারক সার্কিট এবং অ্যান্ড, এবং, নন, এক্সওআর গেটের মতো লজিক গেটের সংমিশ্রণ ব্যবহার করে তৈরি করা যেতে পারে। কাঠামোগত মডেলিংয়ের মতো আমরা প্রতিটি মৌলিক প্রাথমিক বিন্যাসের জন্য বিভিন্ন মডিউল ব্যাখ্যা করি। নিম্নলিখিত কোডে, প্রতিটি গেটের জন্য বিভিন্ন মডিউল সংজ্ঞায়িত করা যায়।

এই মডিউলটি ওআর গেটের জন্য।

ইনপুট: a0, বি 0

আউটপুট: সি 0

শেষ পর্যন্ত, আমরা এই গেটের সুনির্দিষ্ট মডিউলগুলিকে একমাত্র মডিউলে একত্রিত করব। তার জন্য, আমরা এখানে মডিউল ইনস্ট্যান্টেশন ব্যবহার। এখন আমরা কোনও বৈকল্পিক ইনপুট সেটগুলির জন্য কোনও সঠিক মডিউল বা ফাংশনটি প্রতিলিপি করতে চাইলে এই ইনস্ট্যান্টেশনটি ব্যবহার করা যেতে পারে। প্রথমে, আমরা একটি অর্ধ বিয়োগকারকে নকশা করি তারপরে একটি সম্পূর্ণ সাবট্রাক্টর বাস্তবায়নের জন্য এই মডিউলটি ব্যবহৃত হয়। এটি বাস্তবায়নের জন্য, আমরা বাউটের ভেরিয়েবলের জন্য ও / পিএস সংযুক্ত করতে ওআর গেটটি ব্যবহার করি। দ্য পূর্ণ বিয়োগকারীর জন্য ভেরিলোগ কোড নীচে প্রদর্শিত হয়

মডিউল বা_গেট (a0, b0, c0)

ইনপুট a0, বি 0

আউটপুট সি 0

অ্যাসাইন করুন c0 = a0 | খ 0

endmodule

মডিউল xor_gate (এ 1, বি 1, সি 1)

ইনপুট এ 1, বি 1

আউটপুট সি 1

সি 1 = এ 1 ^ বি 1 নির্ধারণ করুন

endmodule

মডিউল এবং_গেট (এ 2, বি 2, সি 2)

ইনপুট এ 2, বি 2

আউটপুট সি 2

সি 2 = এ 2 এবং বি 2 নির্ধারণ করুন

endmodule

মডিউল not_gate (a3, b3)

ইনপুট এ 3

আউটপুট বি 3

বি3 = ~ এ 3 নির্ধারণ করুন

endmodule

মডিউল অর্ধ_স্যাব্র্যাক্টর (এ 4, বি 4, সি 4, ডি 4)

ইনপুট এ 4, বি 4

আউটপুট সি 4, ডি 4

তারের এক্স

xor_gate u1 (এ 4, বি 4, সি 4)

এবং_গেট ইউ 2 (এক্স, বি 4, ডি 4)

not_gate u3 (a4, x)

endmodule

মডিউল পূর্ণ_সেব্র্যাক্টর (এ, বি, বিন, ডি, বাউট)

ইনপুট এ, বি, বিন

আউটপুট ডি, বাউট

তারের পি, কিউ, আর

অর্ধ_স্যাব্র্যাক্টর u4 (এ, বি, পি, কিউ)

অর্ধ_স্যাব্র্যাক্টর u5 (পি, বিন, ডি, আর)

or_gate u6 (কিউ, আর, আউট)

endmodule

4X1 মাল্টিপ্লেক্সার ব্যবহার করে সম্পূর্ণ বিয়োগকারক

বিয়োগের কার্য সম্পাদন দুটির পরিপূরক পদ্ধতির মাধ্যমে করা যেতে পারে। সুতরাং আমাদের একটি 1-এক্সওআর গেট ব্যবহার করা দরকার যা 1-বিট উল্টাতে এবং একটিকে ক্যারি বিটে অন্তর্ভুক্ত করতে ব্যবহৃত হয়। ডিফারেন্সের আউটপুট সম্পূর্ণ সংযোজনকারী সার্কিটের আউটপুট এসইউমের অনুরূপ তবে বারো ও / পি সম্পূর্ণ অ্যাডারের ক্যারি আউটপুটের সাথে সমান নয় তবে এটি বিপরীত পাশাপাশি প্রশংসিত হয়, যেমন - এ - বি = এ + (-বি) = এ + টু বি এর পরিপূরক

4X1 মাল্টিপ্লেক্সার ব্যবহার করে এর নকশাটি নিম্নলিখিত লজিক ডায়াগ্রামে দেখানো হয়েছে। এই নকশাটি নিম্নলিখিত পদক্ষেপগুলি ব্যবহার করে করা যেতে পারে।

4 এক্স 1 মাল্টিপ্লেক্সার

- পদক্ষেপ 1 এ, সাব এবং ধারের মতো দুটি আউটপুট রয়েছে। সুতরাং আমরা 2 মাল্টিপ্লেক্সার নির্বাচন করতে হবে।

- পদক্ষেপ 2 এ, সত্য-সারণীটি কে-ম্যাপের পাশাপাশি প্রয়োগ করা যেতে পারে

- স্টিপি 3 তে দুটি ভেরিয়েবল আপনার নির্বাচিত লাইন হিসাবে নির্বাচিত হতে পারে। উদাহরণস্বরূপ, বি এবং সি এই ক্ষেত্রে রয়েছে।

সঠিক তালিকা

দ্য পূর্ণ বিয়োগকারীর সত্য টেবিল 4X1 মাল্টিপ্লেক্সার ব্যবহার করে সার্কিটটিতে নিম্নলিখিতগুলি অন্তর্ভুক্ত রয়েছে

প্রতি | খ | গ | সাব | ধার |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | ঘ | ঘ | ঘ |

| 0 | ঘ | 0 | ঘ | ঘ |

0 | ঘ | ঘ | 0 | ঘ |

| ঘ | 0 | 0 | ঘ | 0 |

ঘ | 0 | ঘ | 0 | 0 |

| ঘ | ঘ | 0 | 0 | 0 |

ঘ | ঘ | ঘ | ঘ | ঘ |

ডিকোডার ব্যবহার করে সম্পূর্ণ সাবট্রাক্টর

সক্রিয় লো আউটপুটগুলি ব্যবহার করে 3-8 ডিকোডার ব্যবহার করে একটি সম্পূর্ণ সাবট্রাক্টরের ডিজাইনিং করা যেতে পারে। আসুন নিম্নলিখিত লজিক ডায়াগ্রামটি ব্যবহার করে ডিকোডারের কার্যকারিতা ধরে নেওয়া যাক। ডিকোডার 3-8 ডিকোডারে তিনটি ইনপুট অন্তর্ভুক্ত করে। সত্য সারণীর উপর ভিত্তি করে, আমরা পার্থক্য এবং orrowণ গ্রহণের ফলাফলগুলি লিখতে পারি।

উপরের সত্য সারণী থেকে,

সত্য টেবিলের বিভিন্ন ফাংশনের জন্য, মিন্টার্মগুলি 1,2,4,7 হিসাবে লেখা যেতে পারে, এবং একইভাবে, ধারের জন্য, মিনিটারগুলি 1,2,3,7 হিসাবে লেখা যেতে পারে। 3-8 ডিকোডারটিতে তিনটি ইনপুট পাশাপাশি 8 আউটপুটগুলি লিক 0 থেকে 7 নম্বর অন্তর্ভুক্ত করে।

3-থেকে -8 ডিকোডার

যদি বিয়োগকারকের ইনপুটটি 000 হয়, তবে আউটপুট ‘0’ সক্রিয় হবে এবং যদি ইনপুটটি 001 হয়, তবে আউটপুট ‘1’ সক্রিয় হবে।

এখন সাবট্রাক্টরের আউটপুটগুলি 1, 2, 4 এবং 7 থেকে নেওয়া যেতে পারে এটি একটি ন্যানড গেটের সাথে সংযুক্ত করার জন্য, তবে আউটপুটটির পার্থক্য হবে। এই আউটপুটগুলি অন্যান্য নানড লজিক গেটের সাথে সংযুক্ত করা যেতে পারে যেখানে আউটপুট orrowণে পরিবর্তিত হয়।

উদাহরণস্বরূপ, যদি ইনপুটটি 001 হয় তবে আউটপুটটি 1 হবে এর অর্থ এটি সক্রিয়। সুতরাং আউটপুট কম অ্যাক্টিভ থাকে এবং আউটপুট ন্যানড গেট থেকে পাওয়া যায় উচ্চ এবং orrowণ functionণ ফাংশনের মত পার্থক্য ফাংশনটিও উচ্চে পরিবর্তিত হয়। অতএব আমরা পছন্দসই আউটপুট পাই। সুতরাং শেষ পর্যন্ত, ডিকোডার একটি সম্পূর্ণ বিয়োগকারকের মতো কাজ করে।

সুবিধাগুলি এবং অসুবিধাগুলি

দ্য বিয়োগকারীর সুবিধা নিম্নলিখিত অন্তর্ভুক্ত করুন।

- সাবটেক্টর ডিজাইনিং বাস্তবায়ন পাশাপাশি খুব সহজ

- ডিএসপি-র মধ্যে পাওয়ার কাটা (ডিজিটাল সংকেত প্রক্রিয়াকরণ)

- গণনার কাজগুলি উচ্চ গতিতে সম্পন্ন করা যেতে পারে।

দ্য বিয়োগকারক অসুবিধা নিম্নলিখিত অন্তর্ভুক্ত করুন।

- অর্ধ বিয়োগকারীর মধ্যে পূর্ববর্তী পর্ব থেকে orrowণ-সমতুল্য ইনপুট গ্রহণ করার শর্ত নেই।

- সার্কিটের বিলম্বের মধ্য দিয়ে বিয়োগকারকের গতি আংশিক হতে পারে।

অ্যাপ্লিকেশন

কিছু পূর্ণ-বিয়োগকারীর অ্যাপ্লিকেশন নিম্নলিখিত অন্তর্ভুক্ত করুন

- এগুলি সাধারণত সার্কিটের অসুবিধা হ্রাস করতে গ্রাফিক্সের অ্যাপ্লিকেশনগুলির জন্য সিপিইউ এবং জিপিইউ হিসাবে বিয়োগ করতে কম্পিউটারে ALU (পাটিগণিত যুক্তি ইউনিট) এর জন্য নিযুক্ত হয়।

- সাবট্র্যাক্টরগুলি বেশিরভাগ গাণিতিক ফাংশনগুলি যেমন বিয়োগফলের জন্য, বৈদ্যুতিন ক্যালকুলেটরগুলির পাশাপাশি ডিজিটাল ডিভাইসগুলির জন্য ব্যবহৃত হয়।

- এগুলিও প্রযোজ্য বিভিন্ন মাইক্রোকন্ট্রোলার পাটিগণিত বিয়োগ, টাইমার এবং প্রোগ্রাম কাউন্টার (পিসি) জন্য

- সারণী, ঠিকানা, ইত্যাদি গণনা করতে প্রসেসরগুলিতে বিয়োগকারক ব্যবহার করা হয় t

- এটি ডিএসপি এবং নেটওয়ার্কিং ভিত্তিক সিস্টেমগুলির জন্যও কার্যকর।

- এগুলি সার্কিটের জটিলতা হ্রাস করার জন্য গ্রাফিক্স অ্যাপ্লিকেশনগুলির জন্য সিপিইউ এবং জিপিইউয়ের মতো বিয়োগের জন্য কম্পিউটারগুলির মধ্যে মূলত ALU এর জন্য ব্যবহৃত হয়।

- এগুলি মূলত গাণিতিক ক্রিয়াগুলি যেমন ডিজিটাল ডিভাইসগুলির মধ্যে বিয়োগ, ক্যালকুলেটর ইত্যাদির জন্য ব্যবহৃত হয় to

- এই বিয়োগকারীগুলি টাইমার, পিসি (প্রোগ্রামের কাউন্টার) এবং গাণিতিক বিয়োগের জন্য বিভিন্ন মাইক্রোকন্ট্রোলারদের জন্যও উপযুক্ত

- এগুলি ঠিকানা, টেবিল ইত্যাদি গণনা করার জন্য প্রসেসরের জন্য নিযুক্ত করা হয় are

- ন্যান্ড ও এনওআর এর মতো লজিক গেটগুলির সাথে এটি বাস্তবায়ন যে কোনও সম্পূর্ণ সাবট্রেক্টর লজিক সার্কিট দিয়ে করা যেতে পারে কারণ এনওআর এবং ন্যানড উভয় গেটকেই সার্বজনীন গেট বলা হয়।

উপরের তথ্য থেকে, অ্যাডারের মূল্যমানের মাধ্যমে, দুটি আধ আধিকারক সার্কিট এবং এর সারণী ফর্মগুলি ব্যবহার করে সম্পূর্ণ সাবট্র্যাক্টর, এবং কেউ দেখতে পাবে যে পূর্ণ-বিয়োগকারীর ডাউট পুরো অ্যাড্রেটারের সাউটের সাথে সঠিকভাবে মিল রয়েছে। একমাত্র তারতম্যটি হ'ল পূর্ণাঙ্গ বিয়োগকারীর মধ্যে A (ইনপুট ভেরিয়েবল) পরিপূরক। সুতরাং, কেবলমাত্র i / p এ পরিপূরক দ্বারা পূর্ণ-সংযোজক সার্কিটকে একটি পূর্ণ-বিয়োগকারে রূপান্তর করা সম্ভব is লজিক গেটস সর্বশেষ orrowণ-বিট আউটপুট (বিউট) তৈরি করতে।

যে কোনও পূর্ণ সাবট্রাক্টর লজিক সার্কিট ব্যবহার করে, ন্যানড গেটস ব্যবহার করে সম্পূর্ণ সাবট্রেক্টর এবং গেটগুলি ব্যবহার করে সম্পূর্ণ সাবট্রেক্টর প্রয়োগ করা যেতে পারে, যেহেতু ন্যানড এবং এনওআর উভয় গেটই সার্বজনীন গেট হিসাবে বিবেচিত হয়। আপনার জন্য এখানে একটি প্রশ্ন, অর্ধ বিয়োগকার এবং সম্পূর্ণ সাবট্রাক্টরের মধ্যে পার্থক্য কী?