ইসিএল (ইমিটার কাপলড লজিক) প্রথম IBM-তে 1956 সালের আগস্টে হ্যানন এস ইয়োরকে আবিষ্কার করেছিলেন। এই লজিকটি কারেন্ট মোড লজিক নামেও পরিচিত, আইবিএম 7090 এবং 7094 এর কম্পিউটারে ব্যবহৃত হয়। ইসিএল ফ্যামিলির তুলনায় খুব দ্রুত। ডিজিটাল যুক্তি পরিবারগুলি সাধারণত, এই লজিক ফ্যামিলি 1 এনএস-এর কম প্রচার বিলম্ব প্রদান করে। এটি বাইপোলার জংশন ট্রানজিস্টরের উপর ভিত্তি করে একটি লজিক ফ্যামিলি। এটি হল দ্রুততম লজিক ফ্যামিলি সার্কিট যা একটি প্রচলিত লজিক সিস্টেম ডিজাইন করার জন্য অ্যাক্সেসযোগ্য। এই নিবন্ধটি একটি একটি ওভারভিউ আলোচনা ইমিটার যুগল যুক্তি-সার্কিট , অ্যাপ্লিকেশনের সাথে কাজ করা।

Emitter Coupled Logic কি?

ইমিটার-কাপল্ড লজিক সবচেয়ে ভালো বিজেটি -ভিত্তিক লজিক পরিবার প্রচলিত লজিক-সিস্টেম ডিজাইনে ব্যবহৃত হয়। কখনও কখনও, এটিকে কারেন্ট মোড লজিকও বলা হয় যা একটি খুব উচ্চ-গতির ডিজিটাল প্রযুক্তি। সাধারণত, ইসিএলকে দ্রুততম লজিক আইসি হিসাবে বিবেচনা করা হয় যেখানে এটি একটি খুব ছোট ভোল্টেজ সুইং ব্যবহার করে এবং ট্রানজিস্টরগুলিকে স্যাচুরেশন অঞ্চলে প্রবেশ করা এড়িয়ে তার উচ্চ-গতির অপারেশন অর্জন করে।

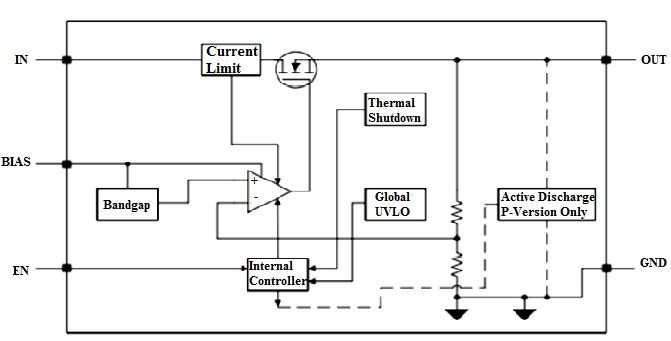

ECL এর বাস্তবায়ন একটি ইতিবাচক সরবরাহ ভোল্টেজ ব্যবহার করে যা PECL বা পজিটিভ-রেফারেন্সড ECL নামে পরিচিত। প্রারম্ভিক ECL গেটগুলিতে, শব্দ প্রতিরোধ ক্ষমতার কারণে একটি নেতিবাচক ভোল্টেজ সরবরাহ ব্যবহার করা হয়। এর পরে, TTL লজিক পরিবারের তুলনায় আরও বেশি সামঞ্জস্যপূর্ণ লজিক স্তরের কারণে ইতিবাচক-উল্লেখিত ECL খুব বিখ্যাত হয়ে ওঠে।

ইমিটার-কাপলড লজিক প্রচুর পরিমাণে স্থির শক্তি নষ্ট করে, তবে এর সামগ্রিক কারেন্টের ব্যবহার তুলনামূলকভাবে কম CMOS উচ্চ ফ্রিকোয়েন্সিতে। সুতরাং, ECL প্রধানত ক্লক-ডিস্ট্রিবিউশন সার্কিট এবং উচ্চ-ফ্রিকোয়েন্সি-ভিত্তিক অ্যাপ্লিকেশনগুলিতে উপকারী।

ইমিটার কাপলড লজিক বৈশিষ্ট্য

ECL-এর বৈশিষ্ট্যগুলি এগুলিকে অনেক উচ্চ-কর্মক্ষমতা-ভিত্তিক অ্যাপ্লিকেশনগুলিতে ব্যবহার করতে সাহায্য করবে।

- ইসিএল দুটি আউটপুট সরবরাহ করে যা সবসময় একে অপরের পরিপূরক কারণ, সার্কিটের কাজটি একটি ডিফারেনশিয়াল এমপ্লিফায়ারের উপর ভিত্তি করে।

- এই লজিক ফ্যামিলিটি মূলত মনোলিথিক ফ্যাব্রিকেশন পদ্ধতির জন্য উপযুক্ত কারণ লজিক লেভেল হল রোধ অনুপাতের একটি ফাংশন।

- ECL পরিবারের ডিভাইসগুলি বাইরের কোনো ইনভার্টার ব্যবহার না করেই প্রস্তাবিত ফাংশনের সঠিক ও পরিপূরক আউটপুট তৈরি করে। ফলস্বরূপ, এটি প্যাকেজের সংখ্যা হ্রাস করে এবং বিদ্যুতের প্রয়োজনীয়তা হ্রাস করে এবং সময় বিলম্বের কারণে সমস্যাগুলিও হ্রাস করে।

- ডিফারেনশিয়াল অ্যামপ্লিফায়ার ডিজাইনে ECL ডিভাইসগুলি বিস্তৃত কর্মক্ষমতা নমনীয়তা অফার করে, তাই ECL সার্কিটগুলি ডিজিটাল এবং লিনিয়ার সার্কিট উভয়ই ব্যবহার করার অনুমতি দেয়।

- ইসিএল গেটের ডিজাইনে সাধারণত উচ্চ এবং কম ইনপুট প্রতিবন্ধকতা থাকে, যা বড় ফ্যান-আউটের পাশাপাশি ড্রাইভের ক্ষমতা অর্জনের জন্য অত্যন্ত সহায়ক।

- ইসিএল ডিভাইসগুলি পাওয়ার সাপ্লাইয়ের নকশাকে সহজ করার জন্য পাওয়ার সাপ্লাইতে একটি ধ্রুবক কারেন্ট তৈরি করে।

- ওপেন এমিটার আউটপুট সহ ECL-এর ডিভাইসগুলি কেবল তাদের ট্রান্সমিশন লাইন ড্রাইভ ক্ষমতা অন্তর্ভুক্ত করার অনুমতি দেয়।

ইমিটার কাপলড লজিক সার্কিট

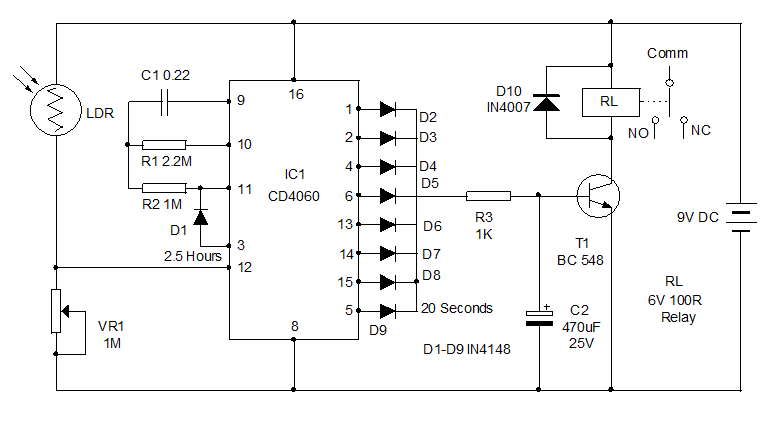

বৈদ্যুতিন সংকেতের মেরু বদল করার জন্য ইমিটার-কাপল্ড লজিক সার্কিট নীচে দেখানো হয়েছে যা প্রতিরোধক এবং ট্রানজিস্টর দিয়ে ডিজাইন করা হয়েছে। এই সার্কিটে, দুটি ট্রানজিস্টরের ইমিটার টার্মিনালগুলি কেবল বর্তমান সীমিত প্রতিরোধের RE-এর সাথে সংযুক্ত থাকে যা ট্রানজিস্টরকে সম্পৃক্ততায় প্রবেশ করা এড়াতে ব্যবহৃত হয়। এখানে ট্রানজিস্টরের আউটপুট ইমিটার টার্মিনালের পরিবর্তে কালেক্টর টার্মিনাল থেকে নেওয়া হয়েছে। এই সার্কিট দুটি আউটপুট Vout (ইনভার্টিং আউটপুট) এবং Vout2 (নন-ইনভার্টিং আউটপুট) এবং ভিনের মতো ইনপুট টার্মিনাল প্রদান করে যেখানে উচ্চ বা নিম্ন ইনপুট দেওয়া হয়। +Vcc = 5V।

ইমিটার কাপলড লজিক কিভাবে কাজ করে?

ইমিটার-কাপল্ড লজিকের কাজ হল, যখনই ECL সার্কিটে উচ্চ ইনপুট দেওয়া হয়, তখনই এটি 'Q1' ট্রানজিস্টর চালু করে এবং Q2 ট্রানজিস্টর বন্ধ করে দেয় কিন্তু Q1 ট্রানজিস্টরটি স্যাচুরেটেড হয় না। সুতরাং এটি VOUT2 আউটপুটকে HIGH এ টেনে আনবে এবং R1 এর মধ্যে ড্রপের কারণে VOUT1 আউটপুটের মান কম হবে।

একইভাবে, যখন ECL-কে দেওয়া VIN মান কম হয়, তখন এটি Q1 ট্রানজিস্টর বন্ধ এবং Q2 ট্রানজিস্টর চালু করবে। সুতরাং, Q2 ট্রানজিস্টর স্যাচুরেশনে চলে যাবে না। সুতরাং এটি VOUT1 আউটপুটকে উচ্চ মান টেনে আনবে এবং R2 প্রতিরোধের মধ্যে ড্রপের কারণে VOUT2 আউটপুট মান কম হবে।

একটি ভোল্টেজ প্রয়োগ করা হলে ট্রানজিস্টর Q1 এবং Q2 কীভাবে চালু এবং বন্ধ হয় তা দেখা যাক।

এই সার্কিটের Q1 এবং Q2 এর মতো দুটি ট্রানজিস্টর একটি সাধারণ ইমিটার রোধ দ্বারা একটি ডিফারেনশিয়াল এমপ্লিফায়ার হিসাবে সংযুক্ত থাকে।

এই উদাহরণ সার্কিটের জন্য ভোল্টেজ সরবরাহ হল VCC = 5.0, VBB = 4.0 এবং VEE = 0 V। ইনপুট উচ্চ এবং নিম্ন-স্তরের মানগুলিকে সহজভাবে 4.4 V এবং 3.6V হিসাবে সংজ্ঞায়িত করা হয়েছে। প্রকৃতপক্ষে, এই সার্কিটটি নিম্ন আউটপুট এবং উচ্চ স্তর তৈরি করে যা 0.6 ভোল্ট বেশি; যাইহোক, এটি বাস্তব ECL সার্কিটের মধ্যে সংশোধন করা হয়।

একবার ভিন হাই হয়ে গেলে, Q1 ট্রানজিস্টর চালু হয়, তবে স্যাচুরেটেড নয় এবং Q2 ট্রানজিস্টরটি বন্ধ হয়ে যায়। সুতরাং, VOUT2 এর মতো আউটপুট ভোল্টেজ R2 রোধের মাধ্যমে 5 V এ টেনে আনা হয় এবং এটি দেখানো যেতে পারে যে R1 রোধ জুড়ে ভোল্টেজ ড্রপ প্রায় 0.8 V যাতে VOUT1 = 4.2 V (LOW)। উপরন্তু VE = VOUT1 – VQ1 => 4.2V – 0.4V = 3.8V যেহেতু ট্রানজিস্টর Q1 সম্পূর্ণরূপে চালু আছে।

একবার ভিন কম হলে, Q2 ট্রানজিস্টর চালু হবে, কিন্তু স্যাচুরেটেড নয় এবং Q1 ট্রানজিস্টর বন্ধ হয়ে যাবে। অতএব, একটি R1 প্রতিরোধক ব্যবহার করে VOUT1 কে 5.0 V এ টেনে আনা হয় এবং এটি দেখানো যেতে পারে যে VOUT2 হল 4.2 V। এছাড়াও VE => VOUT2 – VQ2 => 4.2V – 0.8V => 3.4V যেহেতু ট্রানজিস্টর Q2 চালু আছে।

ইসিএল-এ, দুটি ট্রানজিস্টর কখনই t হিসাবে স্যাচুরেশনে থাকে না ইনপুট/আউটপুট ভোল্টেজের সুইং 0.8v এর মত মোটামুটি ছোট এবং ইনপুট প্রতিবন্ধকতা উচ্চ এবং আউটপুট প্রতিরোধের কম। এটি ইসিএলকে কম প্রচারের বিলম্বের সাথে দ্রুত কাজ করতে সাহায্য করে।

দুটি ইনপুট ইমিটার কাপলড লজিক বা/নর গেট সার্কিট

দুটি ইনপুট ইমিটার যুক্ত লজিক OR/NOR গেট সার্কিট নীচে দেখানো হয়েছে। উপরের বৈদ্যুতিন সংকেতের মেরু বদল সার্কিট পরিবর্তন করে এই সার্কিটটি ডিজাইন করা হয়েছে। পরিবর্তনটি ইনপুট সাইডে একটি অতিরিক্ত ট্রানজিস্টর যোগ করে।

এই সার্কিটের কাজ খুবই সহজ। যখন Q1 এবং Q2 উভয় ট্রানজিস্টরে প্রয়োগ করা ইনপুট কম হয় তখন আউটপুট1 (Vout1) কে উচ্চ মানের করে তুলবে। সুতরাং, এই Vout1 NOR গেটের আউটপুটের সাথে সম্পর্কিত।

একই সাথে, যদি Q3 ট্রানজিস্টর চালু করা হয়, তাহলে এটি দ্বিতীয় আউটপুট (Vout2) কে উচ্চ করে তুলবে। সুতরাং, এই Vou2 আউটপুটটি OR গেট আউটপুটের সাথে মিলে যায়।

একইভাবে, যদি উভয় Q1 এবং Q2 ট্রানজিস্টর ইনপুট উচ্চ হয়, তাহলে এটি Q1 এবং Q2 ট্রানজিস্টর চালু করবে এবং VOUT1 টার্মিনালে কম আউটপুট প্রদান করবে।

যদি এই অপারেশন জুড়ে Q3 ট্রানজিস্টর বন্ধ থাকে তবে এটি VOUT2 টার্মিনালে উচ্চ আউটপুট প্রদান করবে। সুতরাং, OR/NOR গেটের সত্যতা সারণী নীচে দেওয়া হল।

|

ইনপুট |

ইনপুট | বা |

NOR |

|

ক |

খ | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

ইমিটার-কাপল্ড লজিক বৈশিষ্ট্য

ECL এর বৈশিষ্ট্যগুলির মধ্যে নিম্নলিখিতগুলি অন্তর্ভুক্ত রয়েছে।

- TTL-এর তুলনায়, ECL-এর দ্রুত প্রচারের সময় 0.5 থেকে 2 ns পর্যন্ত। কিন্তু, 30 mW এর মত TTL এর তুলনায় ইমিটার কাপলড লজিক পাওয়ার ডিসিপেশন বেশি।

- ECL এর I/O ভোল্টেজ 0.8 এর মত একটি ছোট সুইং আছে।

- ইসিএলের ইনপুট প্রতিবন্ধকতা বেশি এবং আউটপুট প্রতিরোধ ক্ষমতা কম; ফলস্বরূপ, ট্রানজিস্টর খুব দ্রুত তার অবস্থা পরিবর্তন করে।

- ECL-এর ফ্যান-আউট ক্ষমতা বেশি এবং গেট বিলম্ব কম।

- ECL-এর o/p যুক্তি নিম্ন থেকে উচ্চ অবস্থায় পরিবর্তিত হয় কিন্তু এই রাজ্যগুলির জন্য ভোল্টেজের মাত্রা TTL এবং EC-এর মধ্যে পরিবর্তিত হবে।

- ECL এর শব্দ প্রতিরোধ ক্ষমতা 0.4V।

সুবিধাগুলি এবং অসুবিধাগুলি

দ্য ইমিটার-কাপল্ড লজিকের সুবিধা নীচে আলোচনা করা হয়.

- ECL এর ফ্যানআউট 25 যা TTL এর তুলনায় ভাল এবং CMOS এর তুলনায় এটি কম।

- ECL এর গড় প্রচার বিলম্ব সময় 1 থেকে 4 ns যা CMOS এবং উভয়ের তুলনায় ভাল

- টিটিএল এইভাবে একে দ্রুততম লজিক পরিবার বলা হয়।

- যখন বিকিরণকারী BJTs মিলিত হয় যুক্তির পথ সক্রিয় অঞ্চলে কাজ করুন, তারপরে সমস্ত লজিক পরিবারের তুলনায় তাদের সর্বাধিক গতি রয়েছে।

- ইসিএল গেটগুলি পরিপূরক আউটপুট তৈরি করে।

- বর্তমান সুইচিং স্পাইকগুলি পাওয়ার সাপ্লাই লিডগুলিতে নেই৷

- তারযুক্ত-OR ফাংশন প্রদান করতে আউটপুটগুলি যৌথভাবে সংযুক্ত করা যেতে পারে।

- তাপমাত্রার মাধ্যমে ইসিএল-এর প্যারামিটার খুব বেশি পরিবর্তন হয় না।

- না. একটি শুধুমাত্র চিপ থেকে অ্যাক্সেসযোগ্য ফাংশন উচ্চ.

দ্য ইমিটার-কাপল্ড লজিকের অসুবিধা নীচে আলোচনা করা হয়.

- এটির একটি অত্যন্ত কম নয়েজ মার্জিন অর্থাৎ ±200 mV।

- অন্যান্য লজিক গেটের তুলনায় পাওয়ার অপচয় বেশি।

- অন্যান্য লজিক ফ্যামিলির সাথে ইন্টারফেস করতে, লেভেল শিফটার প্রয়োজন।

- ফ্যানআউট ক্যাপাসিটিভ লোডিং সীমাবদ্ধ করে।

- তুলনামুলকভাবে টিটিএল , ECL গেট ব্যয়বহুল।

- CMOS এবং TTL এর তুলনায়, ECL নয়েজ ইমিউনিটি সবচেয়ে খারাপ।

অ্যাপ্লিকেশন

ইমিটার-কাপল্ড লজিকের প্রয়োগের মধ্যে নিম্নলিখিতগুলি অন্তর্ভুক্ত রয়েছে।

- ফাইবার-অপটিক ট্রান্সসিভার ইন্টারফেস, ইথারনেট এবং এটিএম (অ্যাসিনক্রোনাস ট্রান্সফার মোড) নেটওয়ার্কের মতো অত্যন্ত উচ্চ-গতির যোগাযোগ ডিভাইসগুলির মধ্যে ইমিটার-কাপল্ড লজিক একটি লজিক এবং ইন্টারফেস প্রযুক্তি হিসাবে ব্যবহৃত হয়।

- ECL হল BJT-এর উপর ভিত্তি করে একটি লজিক ফ্যামিলি যেখানে তুলনামূলকভাবে ছোট ভোল্টেজ সুইং ব্যবহার করে এবং ট্রানজিস্টরগুলিকে স্যাচুরেশন অঞ্চলে যাওয়া থেকে এড়িয়ে এর উচ্চ-গতির অপারেশন অর্জন করা যেতে পারে।

- ECL IBM 360/91 এর মধ্যে ASLT সার্কিট তৈরিতে ব্যবহৃত হয়।

- ইসিএল একটি বৈদ্যুতিন সংকেতের মেরু বদল ফাংশন অর্জন করার জন্য প্রাথমিক ও মাধ্যমিক ট্রানজিস্টরের মধ্যে একটি একক-এন্ডেড বায়াস i/p এবং ইতিবাচক প্রতিক্রিয়া ব্যবহার করে স্ট্যাক করা ট্রানজিস্টরগুলির ব্যবহার এড়ায়।

- ECL অত্যন্ত উচ্চ-গতির ইলেকট্রনিক্সে ব্যবহৃত হয়।

এইভাবে, এই একটি বিকিরণকারী যুগল যুক্তির একটি ওভারভিউ বা ECL - সার্কিট, কাজ, বৈশিষ্ট্য, বৈশিষ্ট্য, এবং অ্যাপ্লিকেশন। অন্যান্য ডিজিটাল লজিক পরিবারের তুলনায় ECL হল BJT ভিত্তিক খুব দ্রুত লজিক পরিবার। এটি একটি ছোট ভোল্টেজ সুইং ব্যবহার করে এবং স্যাচুরেশন অঞ্চলে ট্রানজিস্টরগুলিকে এড়ানোর মাধ্যমে তার সর্বাধিক গতির ক্রিয়াকলাপ অর্জন করে। এই যুক্তি পরিবার একটি অবিশ্বাস্য 1ns প্রচার বিলম্ব প্রদান করে এবং সর্বশেষ ECL পরিবারগুলিতে, এই বিলম্ব হ্রাস করা হয়। এখানে আপনার জন্য একটি প্রশ্ন, ECL এর বিকল্প নাম কি?